Mesin Mealy: Perbedaan antara revisi

Konten dihapus Konten ditambahkan

k Bot: Migrasi 18 pranala interwiki, karena telah disediakan oleh Wikidata pada item d:Q1126309 |

k Bot: Perubahan kosmetika |

||

| Baris 3: | Baris 3: | ||

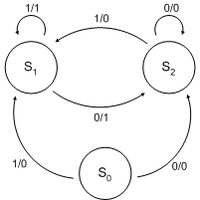

Dalam [[teori komputasi]] sebagai konsep dasar sebuah [[komputer]], '''mesin Mealy''' adalah otomasi fase berhingga (''finite state automaton'' atau ''finite state tranducer'') yang menghasilkan keluaran berdasarkan fase saat itu dan bagian masukan/input. Dalam hal ini, diagram fase (''state diagram'') dari mesin Mealy memiliki [[sinyal]] masukan dan sinyal keluaran untuk tiap transisi. Prinsip ini berbeda dengan [[mesin Moore]] yang hanya menghasilkan keluaran/output pada tiap fase. |

Dalam [[teori komputasi]] sebagai konsep dasar sebuah [[komputer]], '''mesin Mealy''' adalah otomasi fase berhingga (''finite state automaton'' atau ''finite state tranducer'') yang menghasilkan keluaran berdasarkan fase saat itu dan bagian masukan/input. Dalam hal ini, diagram fase (''state diagram'') dari mesin Mealy memiliki [[sinyal]] masukan dan sinyal keluaran untuk tiap transisi. Prinsip ini berbeda dengan [[mesin Moore]] yang hanya menghasilkan keluaran/output pada tiap fase. |

||

Nama Mealy diambil dari "G. H. Mealy" seorang perintis mesin-fase (''state-machine'') yang menulis karangan "A Method for Synthesizing Sequential Circuits" pada tahun 1955. |

Nama Mealy diambil dari "G. H. Mealy" seorang perintis mesin-fase (''state-machine'') yang menulis karangan "A Method for Synthesizing Sequential Circuits" pada tahun 1955. |

||

{{komputer-stub}} |

{{komputer-stub}} |

||

Revisi per 23 Januari 2017 22.37

Dalam teori komputasi sebagai konsep dasar sebuah komputer, mesin Mealy adalah otomasi fase berhingga (finite state automaton atau finite state tranducer) yang menghasilkan keluaran berdasarkan fase saat itu dan bagian masukan/input. Dalam hal ini, diagram fase (state diagram) dari mesin Mealy memiliki sinyal masukan dan sinyal keluaran untuk tiap transisi. Prinsip ini berbeda dengan mesin Moore yang hanya menghasilkan keluaran/output pada tiap fase.

Nama Mealy diambil dari "G. H. Mealy" seorang perintis mesin-fase (state-machine) yang menulis karangan "A Method for Synthesizing Sequential Circuits" pada tahun 1955.